1、NVIC概述

向量中断控制器,简称NVIC,是Cortex-M3不可分离的一部分,它与CM3内核的逻辑紧密耦合。NVIC的寄存器以存储器映射的方式来访问,除了包含控制寄存器和中断处理的控制逻辑之外,NVIC还包含了MPU、SysTick定时器以及调试控制相关的寄存器。

NVIC共支持1至240个外部中断输入(通常外部中断写作IRQs)。具体的数值由芯片厂商在设计芯片时决定。此外,NVIC还支持一个不可屏蔽中断(NMI)输入。NVIC的访问地址是0xE000_E000。所有NVIC的中断控制/状态寄存器都只能在特权级下访问。不过有一个例外——软件触发中断寄存器可以在用户级下访问以产生软件中断。

NVIC的访问地址是0xE000_E000。所有NVIC的中断控制/状态寄存器都只能在特权级下访问。不过有一个例外——软件触发中断寄存器可以在用户级下访问以产生软件中断。所有的中断控制/状态寄存器均可按字/半字/字节的方式访问。此外,还有几个中断掩蔽寄存器也与中断控制密切相关,只能通过MRS/MSR及CPS来访问。

2、中断配置基础

每个外部中断都在NVIC的下列寄存器中“挂号”:

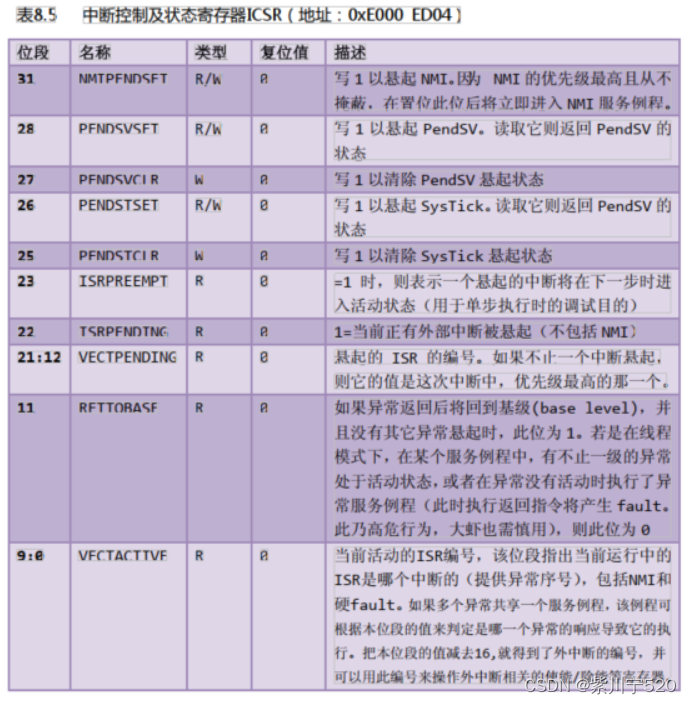

另外,下列寄存器也对中断处理有重大影响

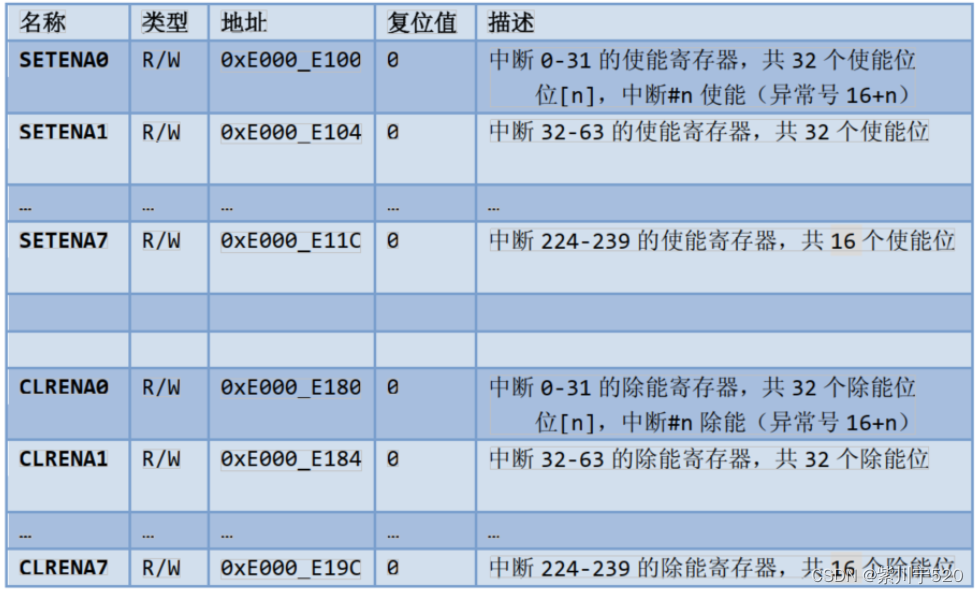

3、中断的使能与除能

中断的使能与除能分别使用各自的寄存器来控制,CM3中可以有240对使能位/除能位(SETENA位/CLRENA位),每个中断拥有一对。这240对分布在8对32位寄存器中(最后一对没有用完)。欲使能一个中断,我们需要写1到对应SETENA的位中;欲除能一个中断,你需要写1到对应的CLRENA位中。如果往它们中写0,则不会有任何效果。SETENA/CLRENA寄存器族如图所示。

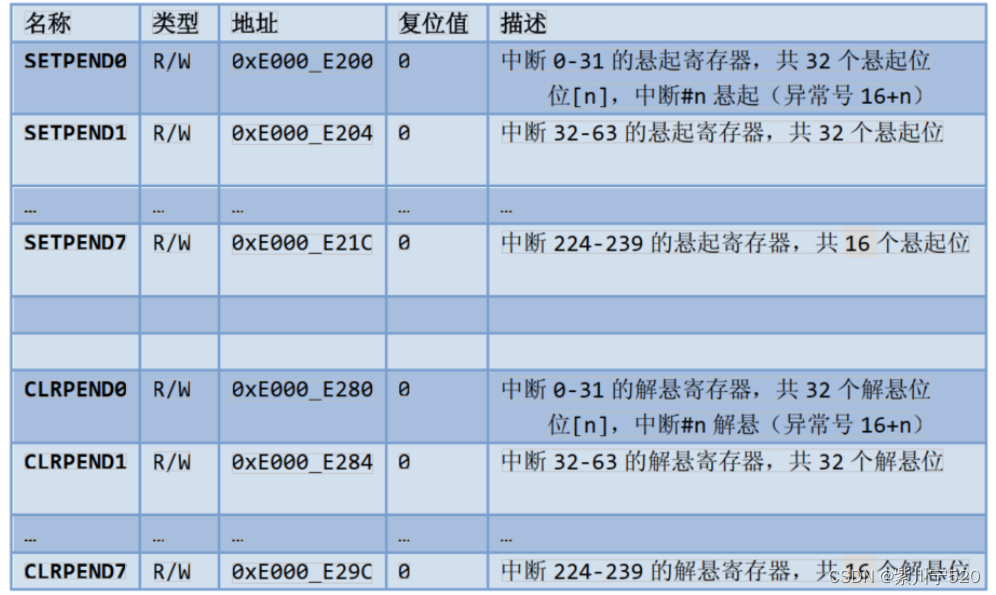

4、中断的悬起与解悬

如果中断发生时,正在处理同级或高优先级异常,或者被掩蔽,则中断不能立即得到响应。此时中断被悬起。中断的悬起状态可以通过“中断设置悬起寄存器(SETPEND)”和“中断悬起清除寄存器(CLRPEND)”来读取,还可以写它们来手工悬起中断。

悬起寄存器和“解悬”寄存器也可以有8对,其用法和用量都与前面介绍的使能/除能寄存器完全相同。SETPEND/CLRPEND寄存器族如图所示。

4.1 优先级

每个外部中断都有一个对应的优先级寄存器,每个寄存器占用8位,但是CM3允许在最“粗线条”的情况下,只使用最高3位。4个相临的优先级寄存器拼成一个32位寄存器。

4.2 活动状态

每个外部中断都有一个活动状态位。在处理器执行了其ISR的第一条指令后,它的活动位就被置1,并且直到ISR返回时才硬件清零。由于支持嵌套,允许高优先级异常抢占某个ISR。然而,哪怕中断被抢占,其活动状态也依然为1。ACTIVE寄存器族如图。

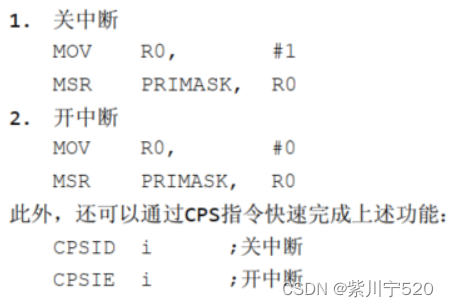

4.3 特殊功能寄存器PRIMASK和FAULTMASK

PRIMASK用于除能在NMI和硬fault之外的所有异常,它有效地把当前优先级改为0(可编程优先级中的最高优先级)。该寄存器可以通过MRS和MSR以下例方式访问:

FAULTMASK更绝,它把当前优先级改为-1。这么一来,连硬fault都被掩蔽了。使用方案与PRIMASK的相似。但要注意的是,FAULTMASK会在异常退出时自动清零。

掩蔽寄存器不能屏蔽NMI,因为NMI是用在最危急的情况下的。

4.4 BASEPRI

在更精巧的设计中,需要对中断掩蔽进行更细腻的控制——只掩蔽优先级低于某一阈值的中断——它们的优先级在数字上大于等于某个数。其值存储在BASEPRI中。如果往BASEPRI中写0,BASEPRI将停止掩蔽任何中断。例如,如果我们需要掩蔽所有优先级不高于0x60的中断,则可以如下编程:

另外,我们还可以使用BASEPRI_MAX这个名字来访问BASEPRI寄存器,它俩其实是同一个寄存器。但是当我们使用这个名字时,会使用一个条件写操作。个中原因如下:尽管它俩在硬件水平上是同一个寄存器,但是生成的机器码不一样,从而硬件的行为也不同:使用BASEPRI时,可以任意设置新的优先级阈值;但是使用BASEPRI_MAX时则“许进不许出”——只允许新的优先级阈值比原来的那个在数值上更小,也就是说,只能一次次地扩大掩蔽范围,反之则不行。就好像绳子打了死结,只会越拉越紧。

为了把掩蔽阈值降低,或者解除掩蔽,需要使用“BASEPRI”这个名字。在用户级下是不得更改BASEPRI寄存器的。与其它和优先级有关的寄存器一样,系统中表达优先级的位数,也同样影响BASEPRI中有意义的位数。

4.5 其他异常的配置寄存器

用法fault,总线fault以及存储器管理fault都是特殊的异常,因此给它们开了小灶。其中,它们的使能控制是通过“系统Handler控制及状态寄存器(SHCSR)”(地址:0xE000_ED24)来实现的。各种faults的悬起状态和大多数系统异常的活动状态也都在该寄存器中。

写这些寄存器时要小心,必须确保对活动位的修改是经过深思熟虑的,决不能粗心修改。否则,如果某个异常的活动位被意外地清零了,其服务例程却不知晓,仍然执行异常返回指令,那么CM3将产生一个fault——在异常服务例程以外做异常返回。

5、软件中断

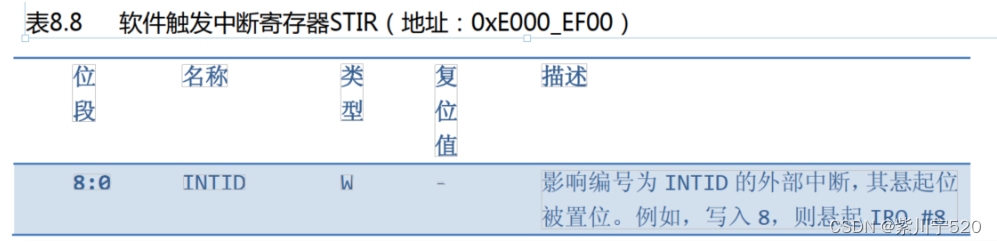

软件中断,包括手工产生的普通中断,能以多种方式产生。最简单的就是使用相应的SETPEND寄存器;而更专业更快捷的作法,则是通过使用软件触发中断寄存器STIR。

注意:系统异常(NMI,faults,PendSV等),不能用此法悬起。而且缺省时根本不允许用户程序改动NVIC寄存器的值。如果确实需要,必须先在NVIC的配置和控制寄存器(0xE000_ED14)中,把比特1(USERSETMPEND)置位,才能允许用户级下访问NVIC的STIR。

6、SysTick定时器

SysTick定时器被捆绑在NVIC中,用于产生SysTick异常(异常号:15)。在以前,操作系统还有所有使用了时基的系统,都必须一个硬件定时器来产生需要的“滴答”中断,作为整个系统的时基。滴答中断对操作系统尤其重要。例如,操作系统可以为多个任务许以不同数目的时间片,确保没有一个任务能霸占系统;或者把每个定时器周期的某个时间范围赐予特定的任务等,还有操作系统提供的各种定时功能,都与这个滴答定时器有关。因此,需要一个定时器来产生周期性的中断,而且最好还让用户程序不能随意访问它的寄存器,以维持操作系统“心跳”的节律。

Cortex-M3处理器内部包含了一个简单的定时器。因为所有的CM3芯片都带有这个定时器,软件在不同CM3器件间的移植工作就得以化简。该定时器的时钟源可以是内部时钟(FCLK,CM3上的自由运行时钟),或者是外部时钟(CM3处理器上的STCLK信号)。不过,STCLK的具体来源则由芯片设计者决定,因此不同产品之间的时钟频率可能会大不相同。因此,需要检视芯片的器件手册来决定选择什么作为时钟源。

SysTick定时器能产生中断,CM3为它专门开出一个异常类型,并且在向量表中有它的一席之地。它使操作系统和其它系统软件在CM3器件间的移植变得简单多了,因为在所有CM3产品间,SysTick的处理方式都是相同的。

校准值寄存器提供了这样一个解决方案:它使系统即使在不同的CM3产品上运行,也能产生恒定的SysTick中断频率。最简单的作法就是:直接把TENMS的值写入重装载寄存器,这样一来,只要没突破系统的“弹性极限”,就能做到每10ms来一次SysTick异常。如果需要其它的SysTick异常周期,则可以根据TENMS的值加以比例计算。只不过,在少数情况下,CM3芯片可能无法准确地提供TENMS的值(如,CM3的校准输入信号被拉低),所以为保险起见,最好在使用TENMS前检查器件 的参考手册。

SysTick定时器除了能服务于操作系统之外,还能用于其它目的:如作为一个闹铃,用于测量时间等。要注意的是,当处理器在调试期间被喊停(halt)时,则SysTick定时器亦将暂停运作。

本文链接:https://my.lmcjl.com/post/2438.html

4 评论